## CNF Project Number: 2800-19 Principal Investigator(s): Huili Grace Xing, Debdeep Jena User(s): Kazuki Nomoto, Lei Li, Austin Hickman

Affiliation(s): School of Electrical and Computer Engineering, Cornell University

Primary Source(s) of Research Funding: ComSenTer

Contact: grace.xing@cornell.edu, kn383@cornell.edu

Primary CNF Tools Used: Autostep i-line stepper, Heidelberg mask writer DWL2000, P7 profilometer, FilMetrics, AFM Veeco Icon, Zeiss SEM, PT770, Oxford 81, Oxford PECVD, Oxford ALD, SC4500 evaporators, AJA sputter deposition tools, RTA AG610, JEOL 9500

## **Abstract:**

Depletion-mode high-electron mobility transistors (HEMTs) based on a quaternary barrier  $In_{0.17}Al_{0.83}N/AlN/GaN$  heterostructure on Si substrate were fabricated. The 55 nm long gate device shows a DC drain current density of 2.8 A/mm, a peak extrinsic transconductance of 660 mS/mm, and balanced current gain cutoff frequency  $f_{\rm T}$  and maximum oscillation frequency  $f_{\rm MAX}$  are 250 and 205 GHz, respectively.

## **Summary of Research:**

Gallium nitride high electron mobility transistors (GaN HEMTs) have high breakdown voltages, high twodimensional electron gas (2DEG) densities, and a high electron saturation velocity. These properties make them ideal for high-power and high-frequency applications, such as switches in power systems and amplifiers in wireless communication systems.

To date, the highest speed GaN HEMTs are demonstrated on SiC substrates, all of which employ regrown ohmic contacts to minimize source/drain resistances. In this report, we have demonstrated the high-frequency and high-power performance capacity of GaN HEMTs on Si substrates. The  $I_{D,MAX'}$  peak  $g_m$  and  $f_T - f_{MAX}$  product are among the best reported for GaN HEMTs on Si, which are very close to the state-of-the-art depletion-mode GaN HEMTs on SiC without a back barrier. This highlight

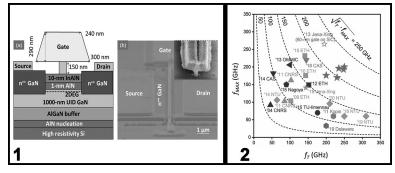

**Figure 1, left**; (a) Schematic cross-section of InAlN/AlN/GaN HEMTs on Si with regrown n<sup>+</sup>GaN contacts. (b) An angled SEM image of a fabricated InAlN/AlN/GaN HEMT with an EBL T-gate. **Figure 2, right:** Comparison of the measured  $f_{T}$  and  $f_{MAX}$  of GaN HEMTs on Si substrates. (See pages vi-vii for full color versions.)

celebrates advances on this front achieved in the CNF and published at IEEE Electron Devices Letters [1].

The InAlN/AlN/GaN HEMT structure consists of a 10 nm In<sub>0.17</sub>Al<sub>0.83</sub>N barrier, a 1 nm AlN spacer (total barrier thickness: 11 nm), an 800 nm unintentionally doped GaN channel, and AlGaN/AlN buffer and nucleation layers on 200-mm-diameter Si substrate, grown by a Propel<sup>®</sup> HVM MOCVD system at Veeco Instruments. Room temperature Hall-effect measurements prior to device fabrication showed a 2DEG sheet concentration of 2.27 × 10<sup>13</sup>/cm<sup>2</sup> and electron mobility of 1430 cm<sup>2</sup>/ V·s, corresponding to a sheet resistance of 206  $\Omega/sq$ .

A schematic cross-section of the InAlN/AlN/GaN HEMT device with regrown  $n^+$  GaN contacts is shown in Figure 1(a). The device fabrication process started

with patterning of a SiO<sub>2</sub> mask for n<sup>+</sup>GaN ohmic regrowth by PA-MBE. The preregrowth etch depth into the HEMT structure was 40 nm, and regrown n<sup>+</sup>GaN was 100 nm with a Si doping level of  $7 \times 10^{19}$  /cm<sup>3</sup>. Non-alloyed ohmic contact of Ti/Au/Ni was deposited by e-beam evaporation. T-shaped Ni/Au (40/200 nm) gates were formed by electronbeam lithography by JEOL 9500, followed by liftoff. TLM measurements yielded a contact resistance of 0.07  $\Omega$ ·mm. The device presented here has a regrown n<sup>+</sup>GaN sourcedrain distance  $L_{\rm sd}$  of 175 nm, a gate width of 2 × 25  $\mu$ m, and a gate length  $L_a$  of 55 nm. Figure 1(b) shows an angled-SEM image of the fabricated InAlN/AlN/GaN HEMT.

ELECTRONICS

The observed maximum drain current  $I_{D,MAX}$  of 2.8 A/ mm and the on resistance  $R_{oN}$  of 0.6  $\Omega$ ·mm, along with the peak transconductance  $g_m^{(n)}$  of 0.66 S/mm, are among the best in GaN HEMTs on Si, comparable to GaN HEMTs on SiC without a back barrier. At low  $V_{DS}$ , these HEMTs typically exhibit a decent  $I_{ON}/I_{OFF}$  ratio ~ 10<sup>5</sup>; HEMT A has the highest gate leakage among all the tested devices, most likely due to processing non-uniformity. The  $f_T/f_{MAX}$  of 250/204 GHz are obtained after deembedding in HEMT A; in comparison, neglecting the short de-embedding test structure renders similar  $f_{\rm T}/f_{\rm MAX}$  values of 245/187 GHz. In Figure 2, the  $f_{\rm T}$  and  $f_{MAX}$  values achieved in this work are compared to other reported GaN HEMTs on Si, as well as the state-of-theart GaN HEMTs on SiC with similar epi-structures and device dimensions (gate length, barrier materials, and its thickness, no back barrier). It can be seen the present HEMTs are clustered near the upper right corner as desired, with  $(f_T \cdot f_{MAX})^{1/2}$  very close to that of the GaN HEMTs on SiC with a comparable gate length.

GaN HEMTs on Si with different geometries were fabricated, measured, and analyzed. The analysis confirms the benefits of  $n^{++}$ -GaN source/drain contacts and T-shaped gates, especially in achieving both high  $f_{MAX}$  and  $f_{T}$ . With the state-of-the-art regrown ohmics, scaled source-drain separation and T-gates, GaN HEMTs on Si achieve comparable metrics with that on SiC in terms of DC and small-signal performance.

## **References:**

[1] L. Li, K. Nomoto, D. Jena, H. G. Xing, et al., "GaN HEMTs on Si with Regrown Contacts and Cutoff/Maximum Oscillation Frequencies of 250/204 GHz"; IEEE Electron Device Lett., 10.1109/ LED.2020.2984727, March. 2020.