# Electrical Characterization of GaAs/InAs Core/Shell Nanowires and InAs Nanotubes

# Jordan Occeña Engineering Physics, University of Tulsa

NNIN iREU Site: Institut Für Bio- Und Nanosysteme (IBN), Forschungszentrum, Jülich, Germany NNIN iREU Principal Investigator: Dr. Mihail Ion Lepsa, Peter Grünberg Institute 9, Forschungszentrum Jülich NNIN iREU Mentor: Torsten Rieger, Peter Grünberg Institute 9, Forschungszentrum Jülich Contact: jordan-occena@utulsa.edu, m.lepsa@fz-juelich.de, t.rieger@fz-juelich.de

## Introduction:

Semiconductor nanowires (NWs) show promise for a variety of nanoelectronic applications due to their high surface area to volume ratio and two-dimensional confinement of charge carriers. The properties of these NWs can be further manipulated through the formation of radial heterostructures. In particular, the use of a gallium arsenide (GaAs) NW core to support an indium arsenide (InAs) shell can potentially result in a tubular conductor suitable for high performance field effect transistors (FETs). The GaAs core can later be removed by selective etching, resulting in an InAs nanotube. Due to its additional surface area and the relaxation of dislocations associated with the GaAs/InAs interface, it is expected that the mobility  $(\mu_{FF})$ of this InAs nanotube would exceed that of the core/shell NW. Here, we investigate and compare the resistivity  $(\rho)$ , electron concentration ( $n_{e}$ ), and  $\mu_{FF}$  of GaAs/InAs core/shell NWs and InAs nanotubes.

### **Experimental Procedure:**

The core/shell NWs studied were grown by molecular beam epitaxy as described by Rieger, et al. [1]. NWs were grown with three different core diameters/shell thicknesses: 110 nm/15 nm, 110 nm/22 nm, 150 nm/18 nm.

In order to extract  $\rho$ ,  $n_e$ , and  $\mu_{FE}$ , top-gate NW FETs were fabricated with hafnium oxide (HfO<sub>2</sub>) as the gate dielectric and GaAs/InAs core/shell NWs as the channel. Core/shell NWs were first coated with 10 nm of HfO<sub>2</sub> by atomic layer deposition. The NWs were then mechanically transferred to a substrate consisting of 200 nm of silicon oxide on degenerately doped silicon.

Optical microscope images of the distribution of the transferred NWs were used to design source, drain, and top-gate contacts for selected NWs. Electron-beam lithography was used to define 1  $\mu$ m long Ti/Au top-gates, which were deposited by electron beam evaporation. After gate deposition, the HfO<sub>2</sub>

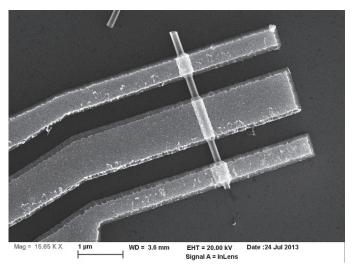

Figure 1: Top-view SEM image of an InAs nanotube FET.

dielectric was removed from the source and drain regions of the NW using a three minute wet etch in 0.05% hydrofluoric acid. Source and drain contacts were then patterned and deposited in the same way as the top-gate contacts. The spacing between adjacent contacts was 500 nm. The electrical properties of the NWs were characterized by two-, three-, and four-probe current-voltage (I-V) measurements on the NW FETs.

After characterization of the core/shell NWs was complete, the GaAs core was selectively etched with a 1:1:40 mixture of  $NH_4OH:H_2O_2:H_2O$  for five minutes to obtain InAs nanotubes, while leaving the FETs intact. Electrical measurements were then repeated for the nanotube FETs. Scanning electron microscope (SEM) images of the nanotube FETs were taken after electrical characterization (Figure 1).

P

н

•2013•NNIN•REU•RESEARCH•ACCOMPLISHMENTS•

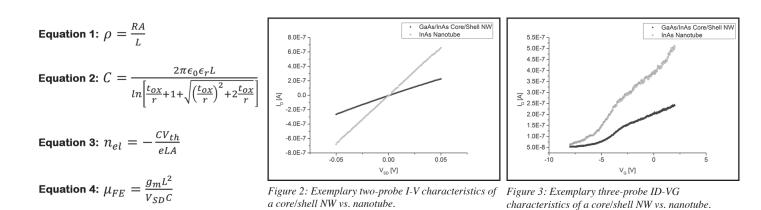

The resistivity of each NW and nanotube was determined by two-probe measurements using Equation 1, where *L* is the length of the NW between source and drain, *R* is the resistance of the NW taken from the I-V curve, and *A* is the portion of the cross-sectional area of the NW that conducts, which is limited to the InAs shell in core/shell NWs due to the band alignment of GaAs and InAs [2]. A small number of four-terminal devices were fabricated to measure the contact resistance, which was found to be negligible in comparison to the resistance of the NWs and was not included in calculations of  $\rho$ .

Values for  $n_e$  and  $\mu_{FE}$  were extracted from three-probe measurements according to Equations 3 and 4, where *C* is the gate capacitance,  $V_{th}$  is the threshold voltage from the  $I_D-V_G$  curve, *e* is the electron charge,  $g_m$  is the transconductance from the  $I_D-V_G$ curve, and  $V_{SD}$  is the voltage between the source and drain, which was held constant at 0.02 V for all three-probe measurements. The gate capacitance, C, was approximated using Equation 2, which is the general form of the gate capacitance for a back-gate NW FET, where  $\varepsilon_0$  is the vacuum permittivity,  $\varepsilon_r$  is the relative permittivity of the gate oxide,  $t_{ox}$  is the gate oxide thickness, and *r* is the NW radius. To account for the use of a top-gate instead of a back-gate, the capacitance values calculated by Equation 2 were increased by 14%, as suggested in Dayeh et al. [3].

## **Results and Discussion:**

For forty-one GaAs/InAs core/shell NWs tested, an average  $\rho$  of 0.14  $\Omega$ •cm was found. After etching of the NW cores to obtain InAs nanotubes, the average  $\rho$  decreased to 0.05  $\Omega$ •cm. An example of two-probe I-V curves for one device before and after etching of the core is shown in Figure 2.

For twenty-nine core/shell NW FETs on which three-probe measurements were conducted, an average  $n_e$  of  $1.33 \times 10^{19}$  cm<sup>-3</sup> and average  $\mu_{FE}$  of 19.2 cm<sup>2</sup>(V•s)<sup>-1</sup> were found. The same devices, after etching of the GaAs core, exhibited an average  $n_e$  of  $1.41 \times 10^{19}$  cm<sup>-3</sup> and an average  $\mu_{FE}$  of 32.0 cm<sup>2</sup> (V•s)<sup>-1</sup>. Sample three-probe I<sub>D</sub>-V<sub>G</sub> curves are shown in Figure 3. For all the parameters, the data showed a large spread most likely related to the device processing.

It was expected that the removal of the GaAs core would allow for the formation of donor-type surface states on the inner surface of the InAs nanotubes in addition to those already present on the outer surface, thus increasing  $n_e$  and decreasing  $\rho$ . The lack of a significant increase in  $n_e$  found experimentally suggests the possible formation of InGaAs at the GaAs/InAs interface. Meanwhile, the small increase in  $\mu_{FE}$  and decrease in  $\rho$  found might still be attributed to relaxation of dislocations associated with the GaAs/InAs interface.

#### Acknowledgements:

A special thanks to Dr. Mihail Ion Lepsa and Torsten Rieger for their guidance and support, as well as to my colleagues at the Forschungszentrum Jülich and the coordinators of the NNIN iREU Program. Thanks also to the NSF for funding this work.

#### **References**:

- [1] Rieger, T., et al. Nano Letters, 12(11), 5559-64.

- [2] Blömers, C., et al. Nanotechnology, 24(3), 035203.

- [3] Dayeh, S., et al. Small, 3(2), 326-32.

Ρ

н

Υ

S